Ques 1: Let R1 and R2 be two 4–bit registers that store numbers in 2’s complement form. For the operation R1 + R2, which one of the following values of R1 and R2 gives an arithmetic overflow?

GATE 2022 Q no 18

(A) R1 = 1011 and R2 = 1110

(B) R1 = 1100 and R2 = 1010

(C) R1 = 0011 and R2 = 0100

(D) R1 = 1001 and R2 = 1111

Ans: (B) R1 = 1100 and R2 = 1010

Solution: If two numbers are represented using 2’s complement method with n bits then condition for overflow is

- If the sign of addends are the different then Overflow never occurs.

- if the sign of addends are the same and the sign of sum is also same as of addend’s sign, then Overflow never occurs.

- if the sign of addends are the same and the sign of sum is different from addend’s sign, then Overflow occurs.

Here in option B,

1100 + 1010 = 10110

After adding carry i.e. 1 to sum i.e 0110, the sum will be 0111

Check the sign i.e MSBs of numbers

Here sign of first number(1100) is -ve, sign of second number(1010) is negative and sign of result (0111) is positive.

So Overflow occurs

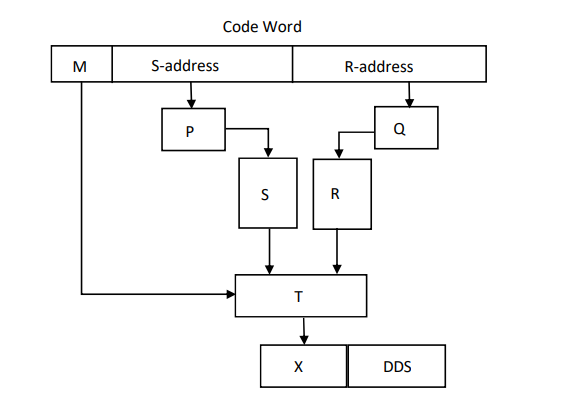

Ques 2: Consider a digital display system (DDS) shown in the figure that displays the contents of register X. A 16-bit code word is used to load a word in X, either from S or from R. S is a 1024-word memory segment and R is a 32-word register file.

Based on the value of mode bit M, T selects an input word to load in X. P and Q interface with the corresponding bits in the code word to choose the addressed word. Which one of the following represents the functionality of P, Q, and T?

GATE 2022 Q no 40

(A) P is 10:1 multiplexer; Q is 5:1 multiplexer; T is 2:1 multiplexer

(B) P is 10:210 decoder; Q is 5:25 decoder; T is 2:1 encoder

(C) P is 10:210 decoder; Q is 5:25 decoder; T is 2:1 multiplexer

(D) P is 1:10 de-multiplexer; Q is 1:5 de-multiplexer; T is 2:1 multiplexer

Ans: (C) P is 10:210 decoder; Q is 5:25 decoder; T is 2:1 multiplexer

Solution:

S is 1024 word memory segment, So it needs 10 address lines.

So, P is a decoder with 10 input lines and 210 output lines.

R is 32 word memory segment, So it needs 5 address lines.

So, Q is a decoder with 5 input lines and 25 output lines.

Based on M, T selects an input word

So it must be a 2:1 Mux

Ques 3: Consider three floating point numbers A, B and C stored in registers RA, RB and RC, respectively as per IEEE-754 single precision floating point format. The 32-bit content stored in these registers (in hexadecimal form) are as follows.

GATE 2022 Q no 41

| RA= 0xC1400000 | RB = 0x42100000 | RC = 0x41400000 |

Which one of the following is FALSE?

(A) A + C = 0

(B) C = A + B

(C) B = 3C

(D) (B – C) > 0

Ans: (B) C = A + B

Solution: Given that Numbers are in IEEE-754 single precision.

Representation is : 1 sign bit, 8 exponent bits and 23 Mantissa Bits

Decimal value=(−1)Sign bit×(1.Mantissa)×(2)exponent−127

RA=0xC1400000=11000001010000000000000000000000

RA=0xC1400000= 1 10000010 10000000000000000000000

Decimal value of RA=(−1)1×(1.1000000000..)×(2)130−127=−(1100)2=−12

Similarly, RB = Ox42100000=01000010000100000000000000000000

RB = Ox42100000=0 10000100 00100000000000000000000

Decimal value of RB=(−1)0×(1.001000000000..)×(2)132−127=−(100100)2=36

And RC=0x41400000=01000001010000000000000000000000

RC=0x41400000=0 10000010 10000000000000000000000

Decimal value of RC=(−1)0×(1.1000000000..)×(2)130−127=(1100)2=12

So, C=A+B is False.