Ques 1: Consider the following processor design characteristics.

GATE 2018 Q no 5

- I. Register-to-register arithmetic operations only

- II. Fixed-length instruction format

- III. Hardwired control unit

Which of the characteristics above are used in the design of a RISC processor?

(A) I and II only

(B) II and III only

(C) I and III only

(D) I, II and III

Ans: (D) I, II and III

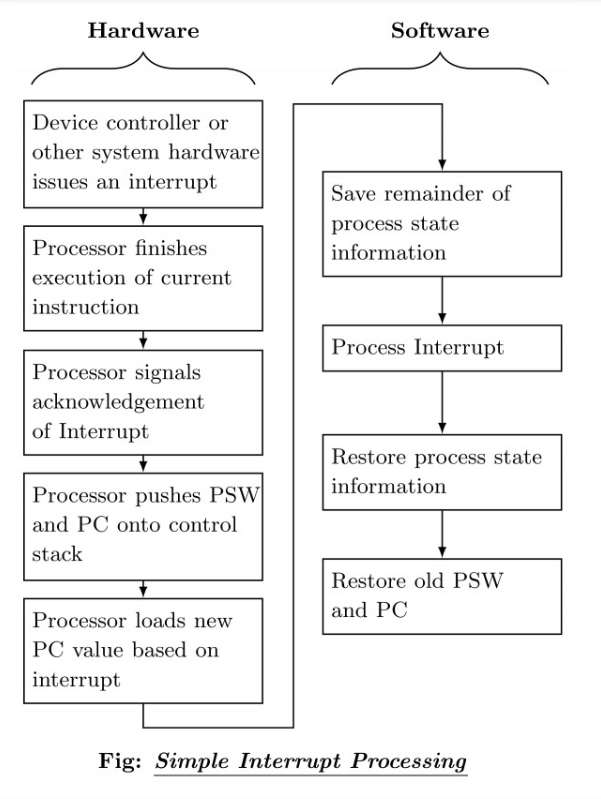

Ques 2: The following are some events that occur after a device controller issues an interrupt while process L is under execution.

GATE 2018 Q no 9

(P) The processor pushes the process status of L onto the control stack.

(Q)The processor finishes the execution of the current instruction.

(R) The processor executes the interrupt service routine.

(S) The processor pops the process status of L from the control stack.

(T) The processor loads the new PC value based on the interrupt.

Which one of the following is the correct order in which the events above occur?

(A) QPTRS

(B) PTRSQ

(C) TRPQS

(D) QTPRS

Ans: (A) QPTRS

Solution:

Ques 3: A 32-bit wide main memory unit with a capacity of 1 GB is built using 256M × 4-bit DRAM chips. The number of rows of memory cells in the DRAM chip is 2 The time taken to perform one refresh operation is 50 nanoseconds. The refresh period is 2 milliseconds. The percentage (rounded to the closest integer) of the time available for performing the memory read/write operations in the main memory unit is _______________.

GATE 2018 Q no 23

Ans: 59 to 60

Solution: One refresh operation takes 50ns

Total number of rows =214

Total time to refresh all Rows =214×50ns=819200ns=0.819200ms

The Refresh Period is 2ms

% Time spent in refresh =Total time to Refresh all Rows/Refresh period∗100

=0.8192ms/2.0ms∗100

=40.96%

% Time spent in Read/Write =100−40.96=59.04%

Ques 4: The size of the physical address space of a processor is 2𝑃 bytes. The word length is 2𝑊 bytes. The capacity of cache memory is 2𝑁 bytes. The size of each cache block is 2𝑀 words. For a 𝐾-way set-associative cache memory, the length (in number of bits) of the tag field is

GATE 2018 Q no 34

(A) 𝑃 − 𝑁 − log2 𝐾

(B) 𝑃 − 𝑁 + log2 𝐾

(C) 𝑃 − 𝑁 − 𝑀 − 𝑊 − log2 𝐾

(D) 𝑃 − 𝑁 − 𝑀 − 𝑊 + log2 𝐾

Ans: (B) 𝑃 − 𝑁 + log2 𝐾

Solution: Physical Address Space=2P Bytes i.e. P bits to represent size of total memory.

Cache Size=2N Byte i.e., N bits to represent Cache memory.

Tag size=2X Bytes i.e., X bits to represent Tag.

Cache is K−way associative.

(Size of Tag)×Cache Size/K=Total Memory Size

2X×2N/K=2P

2X+N−log(K)=2P

X + N – log K =P

X(Size of Tag in bits)=P−N+log(K)

Ques 5: The instruction pipeline of a RISC processor has the following stages: Instruction Fetch (IF), Instruction Decode (ID), Operand Fetch (OF), Perform Operation (PO) and Writeback (WB). The IF, ID, OF and WB stages take 1 clock cycle each for every instruction. Consider a sequence of 100 instructions. In the PO stage, 40 instructions take 3 clock cycles each, 35 instructions take 2 clock cycles each, and the remaining 25 instructions take 1 clock cycle each. Assume that there are no data hazards and no control hazards.

GATE 2018 Q no 50

The number of clock cycles required for completion of execution of the sequence of instructions is _________.

Ans: 219

Solution: Total Instruction =100

Number of stages =5

In normal case total cycles =100+5−1=104 cycles

Now, For PO stage 40 instructions take 3 cycles, 35 take 2 cycles and rest of the 25 take 1 cycle.

That means all other stages are perfectly fine and working with CPI (Clock Cycle Per Instruction)=1

PO stage:

40 instructions take 3 cycles i.e. these instructions are suffering from 2 stall cycle,

35 instructions take 2 cycles i.e. these instructions are suffering from 1 stall cycle,

25 instructions take 1 cycles i.e. these instructions are suffering from 0 stall cycle,

So, extra cycle would be 40∗2+35∗1+25∗0=80+35=115 cycle.

Total cycles = 104+115=219

Ques 6: A processor has 16 integer registers (R0, R1, .. , R15) and 64 floating point registers (F0,F1,… , F63). It uses a 2-byte instruction format. There are four categories of instructions: Type-1, Type-2, Type-3, and Type-4. Type-1 category consists of four instructions, each with 3 integer register operands (3Rs). Type-2 category consists of eight instructions, each with 2 floating point register operands (2Fs). Type-3 category consists of fourteen instructions, each with one integer register operand and one floating point register operand (1R+1F). Type-4 category consists of N instructions, each with a floating point register

operand (1F).

GATE 2018 Q no 51

The maximum value of N is _______________________.

Ans: 32

Solution: We have 2-byte instruction format. So, total number of instruction encodings =216

No. of bits taken by an integer operand (16 possible integer registers)=log216=4

No. of bits taken by a floating point operand (64 possible floating point registers)=log264=6

No. of encodings consumed by Type 1 instructions =4×23×4=214

No. of encodings consumed by Type 2 instructions =8×22×6=215

No. of encodings consumed by Type 3 instructions =14×2(4+6)=14336

No. of encodings left for Type 4=216−(214+215+14336)=2048

No. of different instructions of Type 4=2048/64=32.